WIL CPNX系列

产品特性

◆ 可编程架构

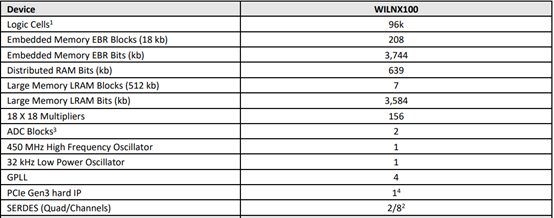

· 100K 逻辑单元

· 156 个 18×18 乘法器数字信号处理(DSP)模块

· 7.3 Mb EBR

· 299 个可编程IO

◆ 可编程IO支持多种协议

· bottom I/O banks支持高性能输入输出接口

· 支持1.8 V Vccio

· 支持多电压(1.0 V, 1.2 V, 1.5 V, and 1.8 V)

· 支持最高 1.5 Gbps的高速差分信号

· 支持LVDS,软核D-PHY Tx/ Rx, LVDS 7:1 Tx/Rx, SLVS Tx/Rx, subLVDS Rx

· 支持SGMII (Gb Ethernet)

· 支持 DDR3/DDR3L 和LPDDR2/LPDDR4, 高达1066 Mbps 数据速率和 64位数据带宽

• 左, 右, 和 顶部 I/O Banks支持Wide Range(WR) IO

· 支持最高 3.3 V Vccio

· 支持多电压:1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V

· 可编程转换速率:slow, medium, fast

· 可控阻抗模式

· 支持LVDS

· 支持热插拔

◆ SerDes

· 单通道速率覆盖 625 Mbps至 10.3125Mbps,最多支持 8 个通道

· 支持多种协议PCS

· 集成高速串行计算机扩展总线标准硬核知识产权

· 以太网

· 10G BASE-R 协议

· SGMII 1.25 Gbps

· XAUI 每通道 3.125 Gbps

· 支持SLVS-EC 1.25 Gbps, 2.5 Gbps and 5 Gbps

· 支持DP/eDP 1.62 Gbps (RBR), 2.7 Gbps (HBR), 5.4 Gbps (HBR2) and 8.1 Gbps (HBR3)

· 支持多速率通用 8b/10b 编码

◆ 功耗模式 —— 低功耗模式与高性能模式

· 支持用户自主选择

· 低功耗模式适用于节能需求或散热受限场景

· 高性能模式适用于高速数据处理场景

◆ 增强型数字信号处理模块

· 集成硬核预加法器

· 支持动态移位,适配人工智能 / 机器学习应用需求

· 可配置为四个 18 × 18, 八个 9 × 9, 两个 18 × 36, 或一个 36 × 36 乘法器

· 每个DSP可实现18×36、双路 18×18 或四路 8×8 MAC运算

◆ 灵活的存储资源

◆ 兼容IEEE1149.1 与 IEEE1532 标准

◆ 内置Reveal逻辑分析功能

◆ 1.0 V内核供电电压

FPGA资源

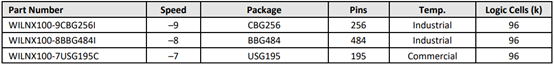

芯片选型